# Evaluation Board and Circuit

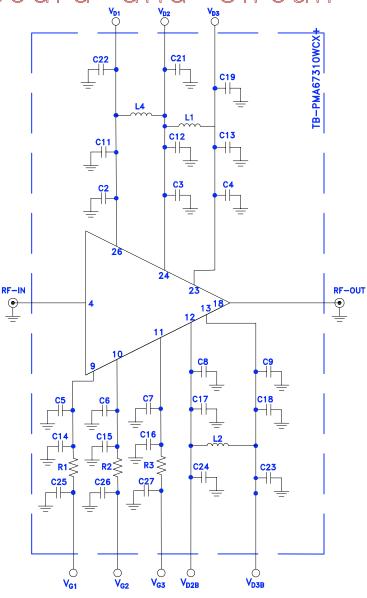

| Component | Size | Value   | PartNumber         | Manufacturer          |

|-----------|------|---------|--------------------|-----------------------|

| R1        | 0402 | 24Ω     | RK73H1ETTP24R0F    | KOA SPEER ELECTRONICS |

| R2        | 0402 | 12Ω     | RK73H1ETTP12R0F    | KOA SPEER ELECTRONICS |

| R3        | 0402 | 0Ω      | RK73Z1ETTP         | KOA SPEER ELECTRONICS |

| C2-C9     | 0402 | 0.001µF | GRM1555C1H102JA01D | MURATA                |

| C11-C18   | 0402 | 0.1µF   | GRM155R71E104KE14D | MURATA                |

| C19-C27   | 0603 | 1µF     | 06035C105KAT2A     | AVX CORPORATION       |

| L1,L2     | 0603 | 1000nH  | 0603AF-33NXJRW     | COILCRAFT             |

| L4        | 0402 | 56nH    | 0402DF-560XJRW     | COILCRAFT             |

## Notes:

- 1. 2.92mm Female Connectors.

- 2. PCB Material: Roger R04003C or equivalent,

Dielectric constant=3.38, Thickness=0.0087±.001 inch

Drain Voltage: VDD; = 8 V

-Check true voltage at the package leads and adjust voltage from the power supply in order to compensate for possible voltage drop across DC cables and meters.

Quiescent current: IDQ12; = 0.75A, IDQ3; = 1 A.

Typical Gate voltage required is between -1 and -0.7 V.

# Note:

- All Drains are tied together thru L1, L4, L2 and a jumper cable connecting top and bottom Drains.

- Gates VG1 and VG2 are tied together and Gate VG3 is separate.

- Current handling of the jumper should be at least 2A.

- It is also recommended to DC probe the unit before turning it on. Just check the DC resistance on the gate side and make sure it is about 500 K $\Omega$ .

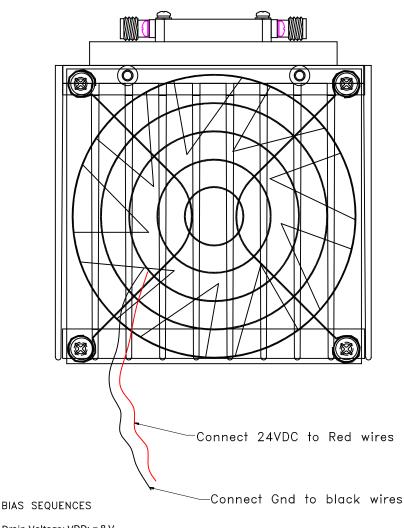

- It is recommended to connect all grounds ((2grounds for Drain & 1 grounds for gate) to the fixture, with a thick enough wire that can handle at least 4A.Pic for reference.

Mini-Circuits

### Bias up sequence:

- 1)Before turning on VDD, apply -2 V on VG12; and VG3 pins.

- 2)Turn on VDD to 8 V.

- 3)Increase VG12 until desired IDQ12(= 0.75A) is reached.

- 4)Increase VG3 until desired IDQ3(=1A) is reached(Total IDQ= IDQ12+IDQ3=1.75A)

- 5)Turn on RF.

### Bias down sequence:

- 1)Turn off RF.

- 2)Decrease VG3 down to -2 V.

- 3)Decrease VG12 to -2 V.

- 4)Turn off VDD.

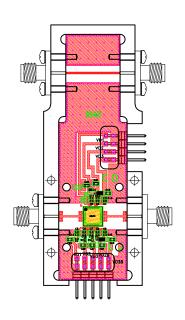

### ALL DIMENSIONS ARE IN INCHES EXCEPT OTHERWISE SPECIFIED

SIZE CODE IDENT DRAWING NO: 15542 TBPMA67310WCX-20+ A -20HSCALE: SHEET: 2

THIS DOCUMENT AND ITS CONTENTS ARE THE PROPERTY OF MINI-CIRCUITS. EXCEPT FOR USE EXPRESSLY GRANTED, IN WRITING, TO ITS VENDORS, VENDEE AND THE UNITED STATES GOVERNMENT, MINI-CIRCUITS RESERVES ALL PROPRIETARY DESIGN, USE, MANUFACTURING AND REPRODUCTION RIGHTS THERETO. THESE CONTENTS SHALL NOT BE USED, DUPLICATED OR DISCLOSED TO ANY OUTSIDE PARTY, IN WHOLE OR IN PART, WITHOUT WRITTEN PERMISSION OF MINI-CIRCUITS.

ASHEETA2.DWG REV:A DATE: 01/12/94

FILE: WTB-PMA67310WC-

OF