## Engineering Development Model

# **Power Splitter/Combiner**

### ADQ-ED12470/1

2 Way-90°

#### **Important Note**

This model has been designed, built and tested in our engineering department. Performance data represents model capability. At present it is a non-catalog model. On request, we can supply a final specification sheet, part number and price/delivery information.

Please click "Back", and then click "Contact Us" for Applications support.

**CASE STYLE: CJ725**

| ELECTRICAL SPECIFICATIONS 50Ω @ +25°C                        |              |      |        |      |       |  |

|--------------------------------------------------------------|--------------|------|--------|------|-------|--|

| Parameter                                                    |              | Min. | Тур.   | Max. | Units |  |

| Frequency                                                    |              | 50   |        | 400  | MHz   |  |

| Isolation                                                    | 50 - 400 MHz |      | 20     |      | dB    |  |

| Insertion Loss<br>Average of Coupled Outputs<br>above 3.0 dB | 50 - 400 MHz |      | 1.00   |      | dB    |  |

| Phase Unbalance                                              | 50 - 400 MHz |      | 92.056 |      | deg.  |  |

| Amplitude Unbalance                                          | 50 - 400 MHz |      | 1.531  |      | dB    |  |

| VSWR                                                         | SUM Port     |      | 1.22   |      | (:1)  |  |

|                                                              | OUT Ports    |      | 1.25   |      | (:1)  |  |

| MAXIMUM RATINGS       |                |  |  |

|-----------------------|----------------|--|--|

| Operating Temperature | -40°C to 85°C  |  |  |

| Storage Temperature   | -55°C to 100°C |  |  |

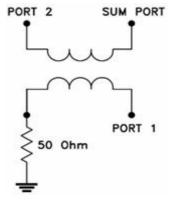

| PIN CONNECTIONS |            |  |  |  |

|-----------------|------------|--|--|--|

| SUM PORT        | 1          |  |  |  |

| PORT 1 (0°)     | 5          |  |  |  |

| PORT 2 (90°)    | 8          |  |  |  |

| 50Ω TERMINATION | 4          |  |  |  |

| GND             | 2, 3, 6, 7 |  |  |  |

#### **Functional Diagram**